# We can't test the kitty unless it exists, so we have to depend on that. # your project, and if there's a Makefile, then they'll expect `make test` # It's good practice to have a `test` target, because people will come to

# *doesn't* re-generate EVERY source file, and then EVERY dest file, # corresponds to the 25.txt file, and then concats them all to kitty. # Note that it is smart enough to re-build JUST the single destfile that

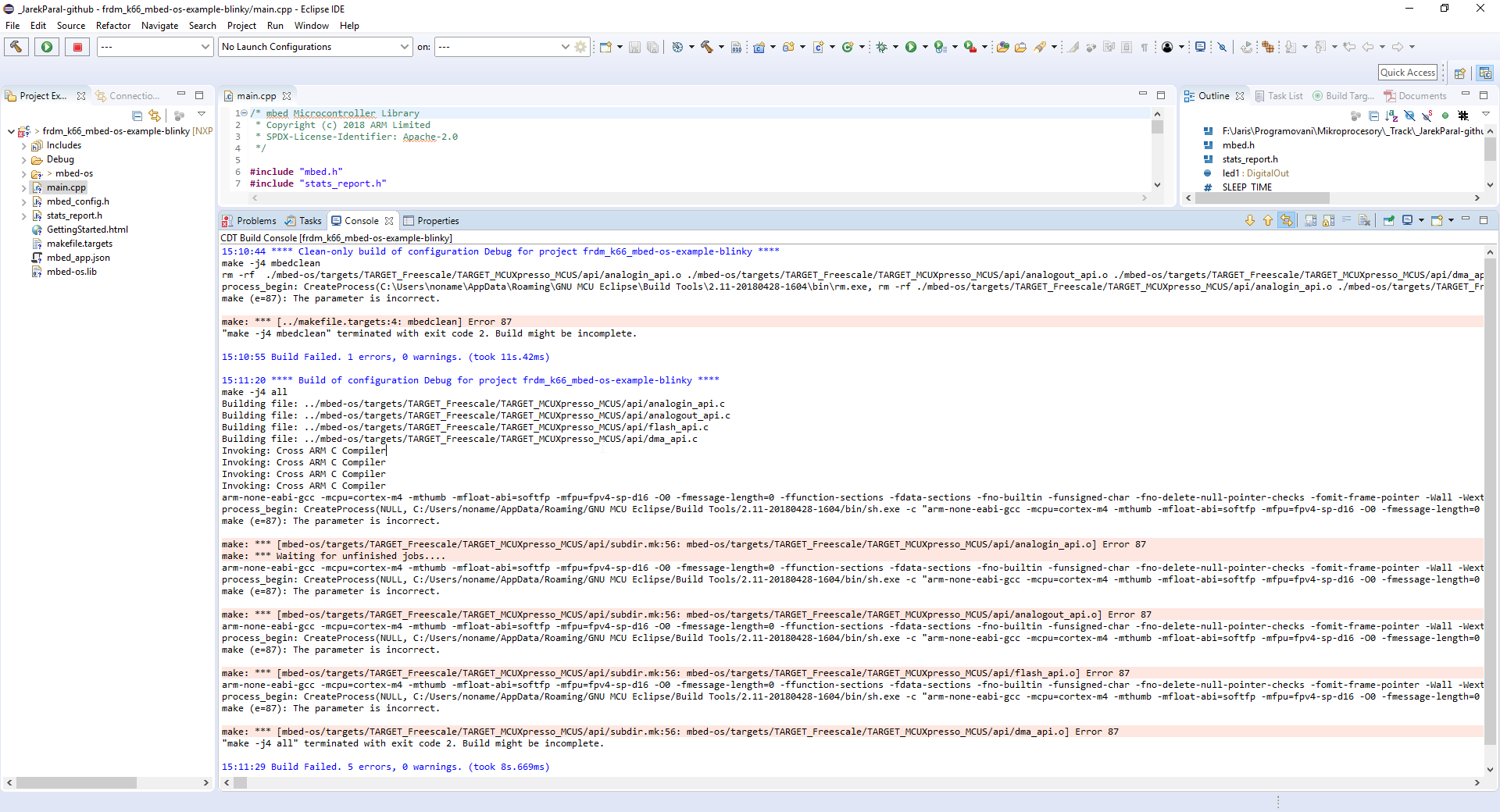

#C MAKEFILE EXAMPLE UPDATE#

# Let's update just ONE of the source files, and see what happens # If you `make kitty` again, it'll say "kitty is up to date" # Then, each destfile depends on a corresponding srcfile You could just as easily say that %.css dependsĭest/ %.txt: src/ -d dest ] || mkdir dest # The destination of any dest/*.txt file is the src/*.txt file with # Also, it has to create the destination folder first. # So, to make a dest file, let's copy a source file into its destination. # Try typing "make source" to make all this happen. # by the %) into the file, like the rule says above. # it'll copy the "stem" value (that is, the number in the filename matched # it can make any of them, it'll first make the src/ dir itself. # Running `make source` will make ALL of the files in the src/ dir. PHONY entry at the very bottom of this file.) # practice to define your phony rules in a.

# depends on all of the srcfiles, and has no other rules. # To not have to run make for each file, we define a "phony" target that # $ Try running `make src/00.txt` and `make src/01.txt` now. # When you type "make foo", then "foo" is the argument. # You can remember this because it's like the list in a # The file that is being made right now by this rule (aka the "target") # Within the ruleset, we can use some special syntax to refer to the input # transform it into the corresponding file of a different pattern. # any files matching a specific pattern, and declare that we're going to We can create one generic rule that handles # It would be SUPER TEDIOUS to create a rule for each one of those. css files, and then link together into a big (This is effectively the same if you have c files we wanted to turn into a corresponding. # Let's say that we were working on a project with 100. # Run `touch source.txt`, or edit the file, and you'll see that # changed, so there's no need to re-build result.txt. # that nothing happens! That's because the dependency, source.txt, hasn't Try running `make result.txt` again, and you'll see # Run `make result.txt` and you'll see it first creates source.txt, and then # Un-comment the next ruleset to fix the "building source.txt"

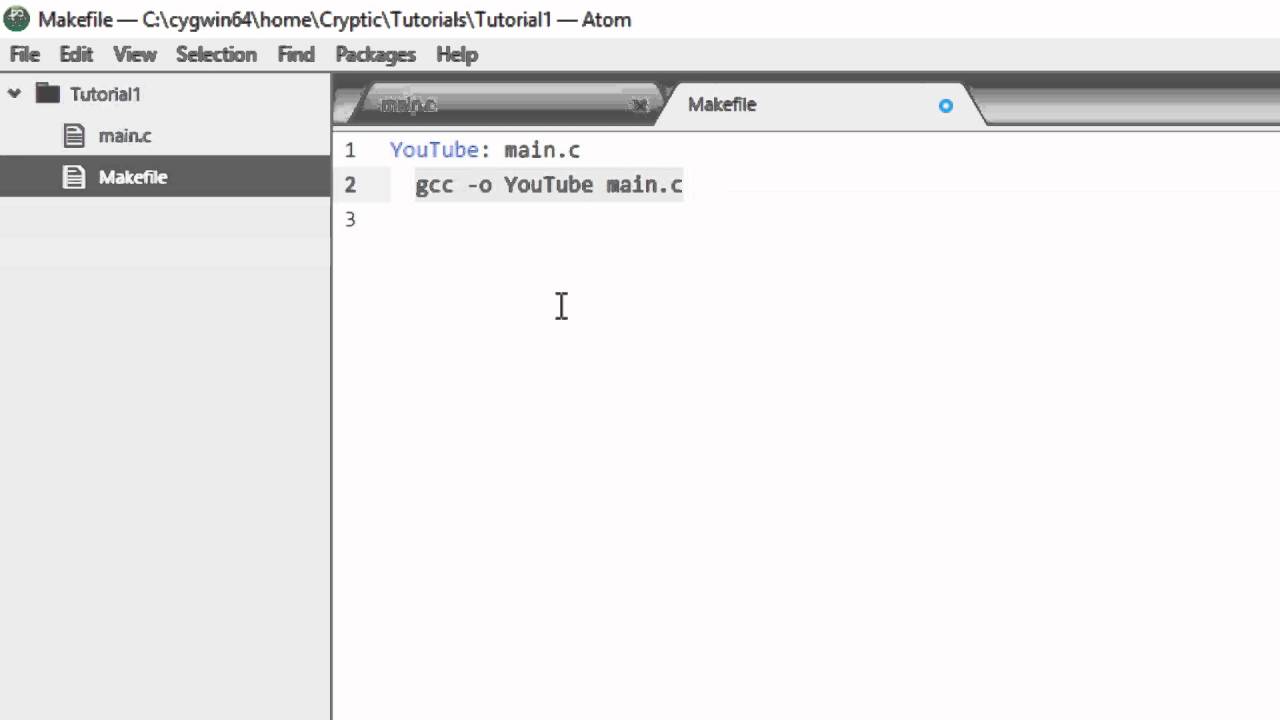

#C MAKEFILE EXAMPLE HOW TO#

# source.txt, but we haven't told it how to get source.txt, and the file is # The problem here is that we've told make to create result.txt from # make: *** No rule to make target `source.txt', needed by `result.txt'. # When we type `make result.txt`, we get an error! Result.txt: "building result.txt from source.txt " # we're going to create a file called "result.txt" which depends on # Now let's try making something that depends on something else. Run `make var-kept` and note the difference. # Let's try running both of the commands in the *same* shell invocation, by # each line of a makefile is parsed first using the makefile syntax, and THEN # Notice that we have to use a double-$ in the command line. # this in action, try running `make var-lost` # So, if you set a variable, it won't be available in the next line! To see # Each line of the command list is run as a separate invocation of the shell. # To suppress the output, we've added signs before each line, above. # UNIX dogma, but without that default, it'd be very difficult to see what This is a departure from the "success should be silent" # By default, make prints out the command before it runs it, so you can see # dir, typing "make" is the same as typing "make tutorial" # By default, the first target is run if you don't specify one. # Type "make" and see what # todo: have this actually run some kind of tutorial "Please read the 'Makefile' file to go through this tutorial " # are also optional, but you have to have one or the other. The prerequisites are optional, and the commands # thing, sort of like a grunt task or an npm package.json script. You can also type `make -f ` to use a different # To do stuff with make, you type `make` in a directory that has a file called # it is actually a highly expressive, efficient, and powerful way to build # You will learn why `make` is so great, and why, despite its "weird" syntax,

0 kommentar(er)

0 kommentar(er)